Cadence Unveils Palladium Z3 and Protium X3 Systems

Cadence

Design Systems, Inc. announced the new Cadence Palladium Z3 Emulation and Protiumâ„¢ X3 FPGA Prototyping systems, a revolutionary

digital twin platform that builds on the success of the industry-leading

Palladium Z2 and Protium X2 systems to tackle escalating system and

semiconductor design complexity, and to accelerate the development timeline for

the most advanced SoCs. Palladium and Protium systems have long been trusted by

market-shaping AI, automotive, hyperscale, networking and mobile chip companies

to deliver the highest throughput pre-silicon hardware debug and pre-silicon

software validation. Targeted at the industry’s largest multi-billion-gate

designs, the new Palladium Z3 and Protium X3 systems set a new standard of

excellence, providing customers with more than a 2X increase in capacity and a

1.5X performance increase compared to previous-generation systems, enabling

faster design bring-up and shortening overall time to market.

“As generational drivers accelerate the need for

system and semiconductor innovation, our customers are facing increasing

challenges to power the most advanced applications,†said Paul Cunningham,

senior vice president and general manager of the System Verification Group at

Cadence. “The third generation Palladium and Protium dynamic duo systems are

core components of the Cadence Verification Suite and seamlessly interface with

the Verisium AI-driven Verification Platform. The Cadence verification full

flow offers our customers the highest verification throughput needed to deliver

their hardware innovations to market faster and to support the rapid

development of new technologies, such as generative AI.â€

The Palladium Z3 and Protium X3 systems offer

increased capacity, and scale from job sizes of 16 million gates up to 48

billion gates, so the largest SoCs can be tested as a whole rather than just

partial models, ensuring proper functionality and performance. The systems are

powered by the NVIDIA BlueField DPU and NVIDIA Quantum InfiniBand networking

platforms and maintain congruency when transitioning between the two systems

and transitioning from virtual to physical interfaces and vice versa. The

Palladium Z3 system accelerates hardware verification, and through functional

and interface congruency, models can be quickly brought up onto the Protium X3

system for accelerated software validation.

“The supercharged Palladium Z3 and Protium X3 are

built to deliver fast pre-silicon verification and validation of the largest

and most complex devices,†said Dhiraj Goswami, corporate vice president,

Hardware System Verification R&D at Cadence. “Our innovative custom silicon

and system architecture, combined with revolutionary modular compile and debug

capabilities enabling multiple turns per day, continues to push the envelope to

meet our customers’ needs, allowing them to solve the world’s toughest

challenges and enable their next generation of innovations to become a

reality.â€

“Building efficient, high-performance AI platforms

requires sophisticated infrastructure and integration across a full stack of

optimized systems and software,†said Scot Schultz, senior director, Networking

at NVIDIA. “Accelerated by NVIDIA networking, the next-generation Cadence

Palladium and Protium systems push the boundaries of capacity and performance

to help enable a new era of generative AI computing.â€

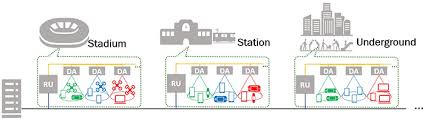

With the Palladium Z3 system’s new domain-specific apps,

users have access to the most complete offering for managing increasing system

and semiconductor design complexity, improving system-level accuracy, and

accelerating low-power verification. The domain-specific apps include the

industry’s first 4-State Emulation App, the Real Number Modeling App, and the

Dynamic Power Analysis App.

“As SoCs become more complex, scalable validation

and verification tools that enable massive software testing before tapeout are

more critical than ever,†said Tran Nguyen, senior director of design services,

Arm. “The latest hardware verification platforms and tools from Cadence are

sparking innovation in Arm IP design for AI, automotive, and data center

applications, and we look forward to how this will benefit our mutual

customers.â€

“Delivering on leadership computing

products requires AMD to bring together a multitude of pre-silicon solutions

and techniques to meet the scale of the verification challenge,†said Alex

Starr, Corporate Fellow, AMD. “Cadence Palladium Z3 and Protium X3 systems add

to our capabilities between emulation and enterprise prototyping to improve

design productivity and meet time-to-market goals. Our collaboration with

Cadence also incorporates the AMD Versalâ„¢ Premium VP1902 adaptive SoC within

the Protium X3 system as well as AMD EPYCâ„¢ processor-based host servers

qualified for both the Palladium Z3 and Protium X3 systems to enable high

capacity with next-level performance and scalability.â€

Leave A Comment